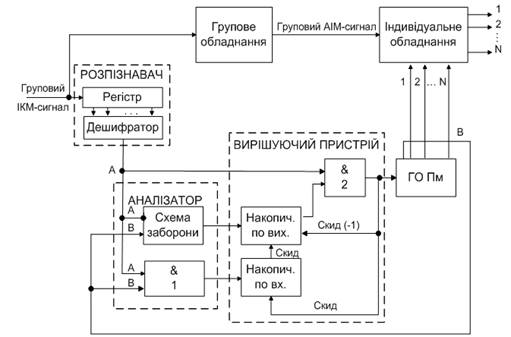

«г≥дно з вищевикладеним приймач синхросигналу маЇ виконувати так≥ функц≥њ:

установку синхрон≥зму п≥сл¤ включенн¤ апаратури ÷—ѕ у роботу; контроль за

станом синхрон≥зму в процес≥ роботи; ви¤вленн¤ збою синхрон≥зму; в≥дновленн¤

стану синхрон≥зму п≥сл¤ кожного збою. ƒл¤ виконанн¤ вказаних функц≥й у склад

приймача синхросигналу, структурна схема ¤кого наведена на рис. 1.30, вход¤ть

розп≥знавач, анал≥затор ≥ вир≥шуючий пристр≥й. ƒодатково на схем≥ наведено √ќпм, ≥ндив≥дуальне

обладнанн¤, ¤к≥ взаЇмод≥ють в процес≥ роботи з приймачем синхросигналу.

–исунок 1.30

–озп≥знавач забезпечуЇ ви¤вленн¤ на¤вност≥ синхросигналу (синхрогрупи) ≥

формуванн¤ ≥мпульсного сигналу за на¤вност≥ синхросигналу у склад≥ вх≥дного

групового ≤ ћ сигналу. –озп≥знавач складаЇтьс¤ з рег≥стра зсуву, розр¤дн≥сть

¤кого сп≥впадаЇ з розр¤дн≥стю синхрогрупи, ≥ дешифратора, настроЇного на

структуру синхрогрупи. «а на¤вност≥ у рег≥стр≥ кодовоњ комб≥нац≥њ з≥

структурою, що сп≥впадаЇ з≥ структурою синхрогрупи, на виход≥ розп≥знавача

з'¤вл¤Їтьс¤ ≥мпульс (ј).

јнал≥затор забезпечуЇ перев≥рку на¤вност≥ циклового синхрон≥зму шл¤хом

перев≥рки на¤вност≥ зб≥гу вих≥дного ≥мпульсу розп≥знавача (ј) з контрольним

≥мпульсом (¬), що формуЇтьс¤ в √ќпм. ѕ≥д час зб≥гу за часом ≥мпульс≥в ј

≥ ¬ спрацьовуЇ схема зб≥гу ![]() †(на њњ виход≥

з'¤вл¤Їтьс¤ ≥мпульс), а за в≥дсутност≥ зб≥гу цих ≥мпульс≥в спрацьовуЇ схема

заборони (на њњ виход≥ з'¤вл¤Їтьс¤ ≥мпульс).

†(на њњ виход≥

з'¤вл¤Їтьс¤ ≥мпульс), а за в≥дсутност≥ зб≥гу цих ≥мпульс≥в спрацьовуЇ схема

заборони (на њњ виход≥ з'¤вл¤Їтьс¤ ≥мпульс).

¬ир≥шуючий

пристр≥й оц≥нюЇ вих≥дн≥ сигнали анал≥затора ≥ приймаЇ р≥шенн¤ про на¤вн≥сть або

в≥дсутн≥сть циклового синхрон≥зму ≥ забезпечуЇ управл≥нн¤ роботою √ќпм у

процес≥ входженн¤ у синхрон≥зм. ќц≥нка на¤вност≥ циклового синхрон≥зму

забезпечуЇтьс¤ за регул¤рн≥стю зб≥гу ≥мпульсу (ј) з виходу розп≥знавача ≥

контрольного ≥мпульсу (¬) з √ќпм, а оц≥нка в≥дсутност≥ синхрон≥зму

забезпечуЇтьс¤ за регул¤рн≥стю в≥дсутност≥ зб≥гу цих ≥мпульс≥в (ј ≥ ¬). ƒл¤

забезпеченн¤ цих оц≥нок у склад вир≥шуючого пристрою вход¤ть накопичувач по

входу ≥ накопичувач по виходу, що ¤вл¤ють собою дв≥йков≥ л≥чильники з≥ скидом.

Ќакопичувач по входу у синхрон≥зм, на вх≥д ¤кого надход¤ть вих≥дн≥ сигнали

схеми зб≥гу ![]() , забезпечуЇ захист приймача синхросигналу в≥д помилкового

входженн¤ у синхрон≥зм, коли на вх≥д розп≥знавача надход¤ть випадков≥

комб≥нац≥њ групового ≤ ћ сигналу, структура ¤ких сп≥впадаЇ з≥ структурою

синхрогрупи. ™мн≥сть накопичувача по входу у синхрон≥зм зазвичай дор≥внюЇ 2...3

розр¤ди.

, забезпечуЇ захист приймача синхросигналу в≥д помилкового

входженн¤ у синхрон≥зм, коли на вх≥д розп≥знавача надход¤ть випадков≥

комб≥нац≥њ групового ≤ ћ сигналу, структура ¤ких сп≥впадаЇ з≥ структурою

синхрогрупи. ™мн≥сть накопичувача по входу у синхрон≥зм зазвичай дор≥внюЇ 2...3

розр¤ди.

Ќакопичувач

по виходу ≥з синхрон≥зму, на вх≥д ¤кого надход¤ть вих≥дн≥ сигнали схеми

заборони, забезпечуЇ захист приймача синхросигналу в≥д помилкового виходу з≥

стану синхрон≥зму, коли перешкоди у л≥н≥йному тракт≥ призвод¤ть до коротких за

часом зм≥н структури синхрогрупи. «азвичай Їмн≥сть накопичувача по виходу ≥з

синхрон≥зму дор≥внюЇ 4...6 розр¤дам.

–озгл¤немо роботу приймача синхросигналу. якщо √ќпм синхрон≥зовано з

роботою √ќпд, то ≥мпульси ј ≥ ¬ сп≥впадають за часом, на виход≥ схеми зб≥гу ![]() †регул¤рно з'¤вл¤ютьс¤

≥мпульси, що п≥дтримують накопичувач по входу у синхрон≥зм у зар¤дженому стан≥.

Ќакопичувач по виходу ≥з синхрон≥зму повн≥стю скинуто. ≤мпульси на виход≥

розп≥знавача (ј), що в≥дпов≥дають випадковим кодовим комб≥нац≥¤м з≥ структурою

синхрогрупи, не впливають на роботу приймача синхросигналу, тому що вони не

сп≥впадають за часом з контрольними ≥мпульсами (¬) в≥д √ќпм.

†регул¤рно з'¤вл¤ютьс¤

≥мпульси, що п≥дтримують накопичувач по входу у синхрон≥зм у зар¤дженому стан≥.

Ќакопичувач по виходу ≥з синхрон≥зму повн≥стю скинуто. ≤мпульси на виход≥

розп≥знавача (ј), що в≥дпов≥дають випадковим кодовим комб≥нац≥¤м з≥ структурою

синхрогрупи, не впливають на роботу приймача синхросигналу, тому що вони не

сп≥впадають за часом з контрольними ≥мпульсами (¬) в≥д √ќпм.

якщо ж

виникають короткочасов≥ збоњ, наприклад, в результат≥ помилок в одному з

цикл≥в, синхросигнал буде перекрученим, то ≥мпульс ј на виход≥ розп≥знавача не

з'¤витьс¤, тому контрольний ≥мпульс ¬ через схему заборони надходить у

накопичувач по виходу ≥з синхрон≥зму. јле стан синхрон≥зму не буде порушеним,

система п≥дтримуватиме стан синхрон≥зму до того часу, поки накопичувач по

виходу ≥з синхрон≥зму буде заповнено частково, а накопичувач по входу

заповнитьс¤ ран≥ше накопичувача по виходу ≥з синхрон≥зму. ¬ результат≥

в≥дбудетьс¤ скид накопичувача по виходу ≥з синхрон≥зму ≥ стан синхрон≥зму не

буде порушеним.

якщо ж

виникають довгочасов≥ збоњ (а також при включенн≥ апаратури), то ≥мпульси ј ≥ ¬

не сп≥впадають, тому ≥мпульс ¬ регул¤рно проходить через схему заборони ≥

зар¤джаЇ накопичувач по виходу ≥з синхрон≥зму за к≥льк≥сть цикл≥в, що дор≥внюЇ

Їмност≥ цього накопичувача (4 ... 6 розр¤д≥в). ≤мпульси ј д≥ють на

заборон¤ючому вход≥ схеми заборони, тому у процес≥ накопиченн¤ участ≥ не

приймають. «ар¤джений накопичувач по виходу з синхрон≥зму в≥дкриваЇ по одному з

вход≥в схеми зб≥гу ![]() . ¬ результат≥ ≥мпульс ј з виходу розп≥знавача, що надходить

на другий вх≥д схеми

. ¬ результат≥ ≥мпульс ј з виходу розп≥знавача, що надходить

на другий вх≥д схеми ![]() , проходить через цю схему ≥ встановлюЇ √ќпм у положенн¤, що зб≥гаЇтьс¤

з положенн¤м √ќпд (¤кщо ≥мпульс ј в≥дпов≥даЇ ≥стинн≥й синхрогруп≥), або в ≥нше

положенн¤ (¤кщо ≥мпульс ј сформовано з хибноњ синхрогрупи). р≥м установки √ќпм

≥мпульс з виходу схеми

, проходить через цю схему ≥ встановлюЇ √ќпм у положенн¤, що зб≥гаЇтьс¤

з положенн¤м √ќпд (¤кщо ≥мпульс ј в≥дпов≥даЇ ≥стинн≥й синхрогруп≥), або в ≥нше

положенн¤ (¤кщо ≥мпульс ј сформовано з хибноњ синхрогрупи). р≥м установки √ќпм

≥мпульс з виходу схеми ![]() †скидаЇ повн≥стю

накопичувач по входу у синхрон≥зм ≥ зменшуЇ зм≥ст накопичувача по виходу ≥з

синхрон≥зму на одиницю.

†скидаЇ повн≥стю

накопичувач по входу у синхрон≥зм ≥ зменшуЇ зм≥ст накопичувача по виходу ≥з

синхрон≥зму на одиницю.

якщо установка √ќпм зд≥йснювалас¤ ≥мпульсом ј, що в≥дпов≥даЇ ≥стинн≥й

синхрогруп≥, то у чергових циклах ≥мпульс ¬ зб≥гатиметьс¤ з ≥мпульсом ј, тому

на виход≥ схеми зб≥гу ![]() †регул¤рно з'¤вл¤тиметьс¤

≥мпульс, що забезпечуЇ зар¤д накопичувача по входу в синхрон≥зм. «ар¤джений

накопичувач по входу скидаЇ до нул¤ накопичувач по виходу ≥з синхрон≥зму. ѕ≥сл¤

входженн¤ у синхрон≥зм ≥ в≥дсутност≥ збоњв п≥дтримуЇтьс¤ стан √ќпм однаковий з≥

станом √ќпд. ” стан≥ синхрон≥зац≥њ накопичувач по входу повн≥стю зар¤джений,

накопичувач по виходу ≥з синхрон≥зму повн≥стю скинутий, тому схема

†регул¤рно з'¤вл¤тиметьс¤

≥мпульс, що забезпечуЇ зар¤д накопичувача по входу в синхрон≥зм. «ар¤джений

накопичувач по входу скидаЇ до нул¤ накопичувач по виходу ≥з синхрон≥зму. ѕ≥сл¤

входженн¤ у синхрон≥зм ≥ в≥дсутност≥ збоњв п≥дтримуЇтьс¤ стан √ќпм однаковий з≥

станом √ќпд. ” стан≥ синхрон≥зац≥њ накопичувач по входу повн≥стю зар¤джений,

накопичувач по виходу ≥з синхрон≥зму повн≥стю скинутий, тому схема ![]() †зачинена, що захищаЇ

в≥д надходженн¤ на вх≥д √ќпм будь-¤ких синхросигнал≥в ј (¤к ≥стинних, так ≥

хибних).

†зачинена, що захищаЇ

в≥д надходженн¤ на вх≥д √ќпм будь-¤ких синхросигнал≥в ј (¤к ≥стинних, так ≥

хибних).

якщо ж установка √ќпм зд≥йснювалас¤ хибним синхросигналом, то вже у

черговому цикл≥ повн≥стю зар¤джаЇтьс¤ накопичувач по виходу ≥з синхрон≥зму,

в≥дчин¤Їтьс¤ схема ![]() †≥ черговий ≥мпульс ј

≥з розп≥знавача знову установлюЇ √ќпм ≥ накопичувач≥ в ран≥ше зазначений стан.

ѕроцес продовжуЇтьс¤ до дос¤гненн¤ циклового синхрон≥зму.

†≥ черговий ≥мпульс ј

≥з розп≥знавача знову установлюЇ √ќпм ≥ накопичувач≥ в ран≥ше зазначений стан.

ѕроцес продовжуЇтьс¤ до дос¤гненн¤ циклового синхрон≥зму.

–озгл¤нутий

спос≥б побудови приймача синхросигналу маЇ суттЇв≥ недол≥ки. ѕерший з них

пол¤гаЇ в тому, що процес пошуку синхросигналу починаЇтьс¤ п≥сл¤ заповненн¤

накопичувача по виходу ≥з синхрон≥зму, що призводить до зб≥льшенн¤ часу

входженн¤ у цикловий синхрон≥зм.

ƒругим

недол≥ком Ї ф≥ксован≥ Їмност≥ накопичувач≥в по входу в синхрон≥зм ≥ виходу з

синхрон≥зму, що не дозвол¤Ї оптим≥зувати сп≥вв≥дношенн¤ м≥ж часом входженн¤ у

синхрон≥зм ≥ завадост≥йк≥стю. ƒ≥йсно, з≥ зб≥льшенн¤м ≥мов≥рност≥ помилок у

л≥н≥йному тракт≥, пор≥вн¤но з розрахованим значенн¤м, час утриманн¤ стану

синхрон≥зму стаЇ менше за той, що вимагаЇтьс¤, ≥ навпаки Ц з≥ зменшенн¤м

≥мов≥рност≥ помилок виникаЇ необірунтований запас часу утриманн¤ стану

синхрон≥зму.

ѕерший недол≥к усуваЇтьс¤ шл¤хом об'Їднанн¤ за часом процес≥в накопиченн¤

по виходу ≥з синхрон≥зму ≥ пошуку синхрон≥зму. ѕриймач синхросигналу, що маЇ

окрему схему пошуку ≥ схему утриманн¤ синхрон≥зму, забезпечуЇ зменшенн¤

середнього часу входженн¤ у синхрон≥зм ≥ зб≥льшенн¤ середнього часу управл≥нн¤

синхрон≥зму.

ƒругий недол≥к може бути усунений

шл¤хом використанн¤ накопичувач≥в, Їмн≥сть ¤ких може зм≥нюватис¤ в≥дпов≥дно до

зм≥ни ймов≥рност≥ помилки у л≥н≥йному тракт≥: з≥ зменшенн¤м ймов≥рност≥ помилки

зменшуЇтьс¤ Їмн≥сть накопичувача по виходу ≥з синхрон≥зму, а з≥ зб≥льшенн¤м

ймов≥рност≥ помилок зменшуЇтьс¤ Їмн≥сть накопичувача по входу в синхрон≥зм.

“ак≥ приймач≥ синхросигналу Ї адаптивними ≥ широко використовуютьс¤ в ÷—ѕ.